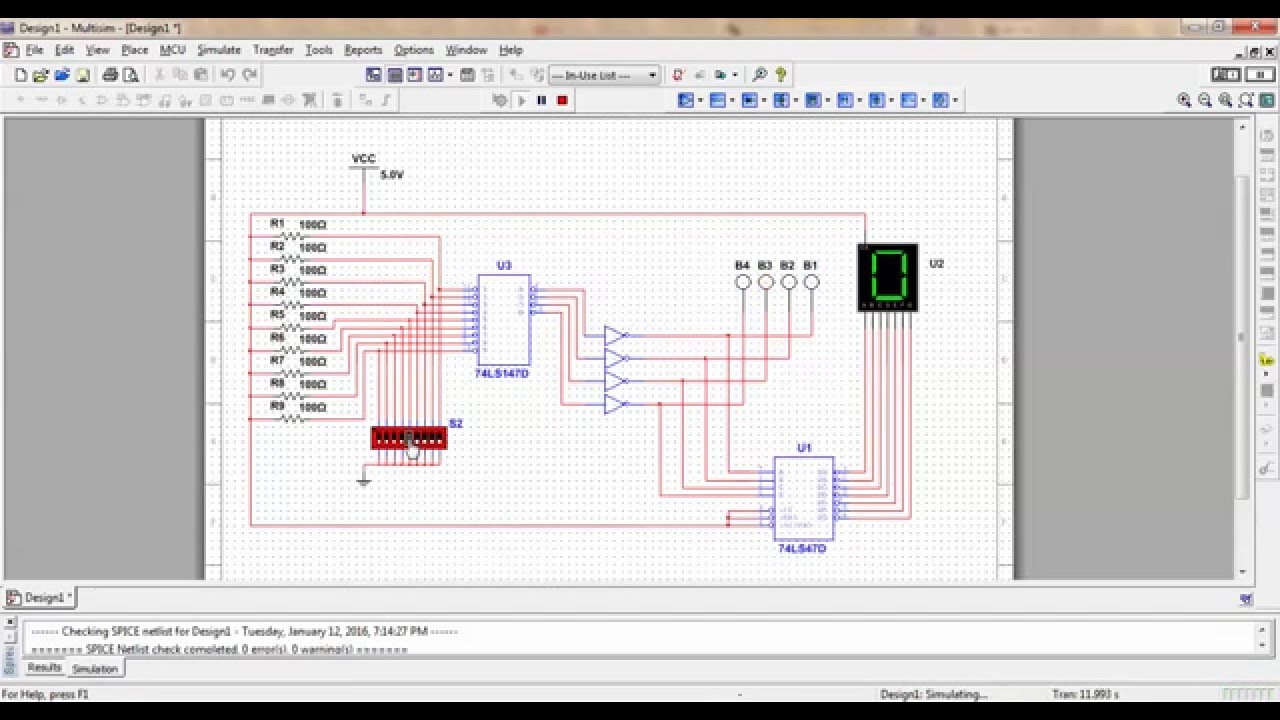

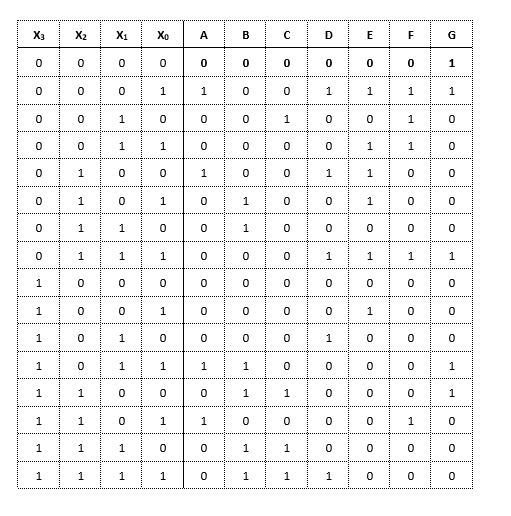

All the other binary combinations for number 10-15 can be considered as don’t care. Repeat this until youve programmed all the first 16 bytes. Program each byte of the first 16 bytes so that for address 0000 it lights up 0 on 7-seg display, for address 0001 it lights up 1 on the 7-seg display, and. We will tabulate which segments should be lit up in order to show the decimal numbers on out 7 segment display. Connect the four binary numbers to be converted to the hex to the first 4 address lines and the data lines to the 7-seg pins. Actually, most 7-segment displays contain eight internal LED’s as the eigth one is used for a decimal point, usually in. By simplifying Boolean expression to implement structural design and behavioral design.įor constructing BCD to 7 segment display, first construct truth table and simplify them to Boolean expression using K Map and finally build the combinational circuit. First we will develop the combinational logic to implement this BCD to 7 segment display decoder. As its name suggests, a 7-segment display consists of seven segments, meaning it consists of seven light emitting diodes or LED’s, which together can be used to form one complete digit on the display. module ctr (counter,reset,clk)//out output reg 13:0 counter // output reg out input reset. Following is a sample code, this may not be the optimum version. After reaching 0630, it gets reset and it can optionally give an out pulse indication. VHDL Code BCD to 7 Segment Display decoder can be implemented in 2 ways. The counter should count down from 9999 to 0630 on every clock pulse.

Seven display consist of 7 led segments to display 0 to 9 and A to F. The BCD to 7 Segment Decoder converts 4 bit binary to 7 bit control signal which can be displayed on 7 segment display. I recently finished a 4 bit adder project and I wanted to 'extend' it.Right now,the output is represented by 4 leds(1 for each bit).I want to display the answer as a decimal in a seven segment display.The biggest value that the adder can output is 15(since it is a 4 bit adder).I have two single digit seven segment displays. Testbench waveform for BCD to 7 Segment Display Decoder Abstract: This ’blog describes using a ValentF(x) LOGI-EDU board to make a 4-digit BCD (binary-coded decimal) counter using LOGI-EDU’s 4-digit seven-segment LED module.I used both LOGI-Pi and LOGI-Bone FPGA boards to implement the BCD counter logic.VHDL Testbench Code for BCD to 7 segment display.VHDL Code for BCD to 7 segment display using Case Statement.VHDL Code for BCD to 7 segment display using Combinatorial logic.BCD to 7 segment display Decoder Circuit.BCD to 7 segment display Decoder Truth Table.Signal refresh_counter : STD_LOGIC_VECTOR ( 19 downto 0) counting decimal number to be displayed on 4-digit 7-segment display signal LED_BCD : STD_LOGIC_VECTOR ( 3 downto 0) one second enable for counting numbers signal displayed_number : STD_LOGIC_VECTOR ( 15 downto 0) LAB 3 Verilog for Combinatorial Circuits Goals Learn how to design combinatorial circuits using Verilog Design a simple circuit that takes a 4-bit binary number and drive the 7-segment display so that it is displayed using hexadecimal format.

In this the seven segment display controller is explained.

A seven segment display controller is necessary to display BCD digits. counter for generating 1-second clock enable signal one_second_enable : std_logic Seven segment displays are having seven segments and using these seven segments any digits from 0 to 9 can displayed. LED_out : out STD_LOGIC_VECTOR ( 6 downto 0)) - Cathode patterns of 7-segment display end seven_segment_display_VHDL Īrchitecture Behavioral of seven_segment_display_VHDL is signal one_second_counter : STD_LOGIC_VECTOR ( 27 downto 0) : FPGA projects, Verilog projects, VHDL projects - VHDL code for seven-segment display on Basys 3 FPGA library IEEE Įntity seven_segment_display_VHDL is Port ( clock_100Mhz : in STD_LOGIC - 100Mhz clock on Basys 3 FPGA boardĪnode_Activate : out STD_LOGIC_VECTOR ( 3 downto 0) - 4 Anode signals VHDL code for seven-segment display on Bays 3 FPGA: the fourth hex digit of the 16-bit number end case Įnd process Now, let's use it for displaying a counting hexadecimal number on the 4-digit seven-segment display on Basys 3 FPGA. begingroup You have 8 input bits (3 bits each for operand A and B, and 2 bits to select 1 of 4 opcodes), and 14 outputs: 7 for each segment, 16 if you include the decimal points. LED_BCD <= displayed_number( 3 downto 0) In this paper a circuit that can display the decimal equivalent of an n-bit binary number is designed and it’s behavior is described using Verilog Hardware. activate LED4 and Deactivate LED2, LED3, LED1 7-segment display controller - generate refresh period of 10.5ms process(clock_100Mhz,reset)

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed